** 여기서의 반도체란? 반도체 물질이 아닌, 트랜지스터와 같은 반도체 소자를 의미한다.

1. 역사

- 컴퓨터와 같은 해석기관은, "무언가의 흐름을 제어하는 도구"를 여러 개 연결하여 만들어 낼 수 있다.

- 컴퓨터의 시초라 할 수 있는 에니악은 진공관을 기반으로 전기 신호를 제어했다.

- 최초의 트랜지스터 BJT는 일정 수준 이상의 전압을 받으면 컬렉터와 이미터 사이의 전류 흐름을 변경한다. 즉, 전기로 전기의 흐름을 제어한다.

- 1959년 개발된 모스펫, MOSFET은 전계 효과 트랜지스터로, 실리콘 표면에 산화, 식각, 세정 처리를 거쳐 제작된다.

- 실리콘 웨이퍼 표면에 수만개 모스펫 생산이 가능해 이전 트랜지스터의 성능과 생산 효율이 대폭 상승한다.

- 노광 해상도가 높을수록 모스펫 크기를 감소시켜 면적당 모스펫 수를 늘릴 수 있다.

금속 산화막 반도체 전계효과 트랜지스터(영어: metal-oxide-semiconductor field-effect transistor)는 디지털 회로와 아날로그 회로에서 가장 일반적인 전계효과 트랜지스터 (FET)이다. 줄여서 MOSFET(한국어: 모스펫)이라고도 한다. 모스펫은 N형 반도체나 P형 반도체 재료 (반도체소자 참조)의 채널로 구성되어 있고, 이 재료에 따라서 크게 엔모스펫 (NMOSFET)나 피모스펫 (PMOSFET), 두 가지를 모두 가진 소자를 씨모스펫(cMOSFET, complementary MOSFET)으로 분류한다. (또한 일반적으로 nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, p-MOS FET. etc..라고도 함)

Source: Wikipedia

The invention in its preferred form comprises a semiconductor wafer, typically silicon, including first, second and third regions defining respectively first and second p-n junctions which intersect a major surface of the wafer. This major surface of the wafer is coated with a suitable dielectric, typically a thermally grown silicon dioxide coating for a silicon wafer, and an electrode is connected to the surface of this oxide coating so as to extend beyond the line of intersection with the surface of the two p-n junctions. A first bias voltage is applied between ohmic contacts to the first and third regions poled to forward bias the first p-n junction and to reverse bias the second. A second bias voltage is applied between the electrode to the oxide coating and the contact to the third region. The electric field across the oxide coating is-the result of this second bias and varies in response to variations in the voltage between the two substantially ohmic contacts.

Electric field controlled semiconductor device, US3102230A

Inventor: Kahng Dawon / Current Assignee: AT&T Corp

https://patents.google.com/patent/US3102230A/en

[반도체 집적회로의 역사]

진화의 시작을 알린 트랜지스터 :

- 트랜지스터의 발견 : 1947년, 미국 최대 전화 통신 회사 AT&T 벨 연구소 연구원들은 반도체 격자구조의 조각에 도체선(전기가 흐르는데 사용되는 선)을 접촉시키면 전기 신호가 증폭한다는 사실을 발견

- 트랜지스터의 문제 : 전자제품의 기능이 많아지면서 트랜지스터와 저항, 다이오드, 캐패시터 등 연결해 주어야 하는 부분이 기하급수적으로 증가

- 집적회로의 탄생 : 1958년 美 텍사스 인스트루먼트(TI) 잭 킬비(Jack Kilby)가 집적회로를 개발. 복잡한 전자 부품들을 정밀하게 만들어 작은 평면에 인쇄하듯 찍어내 차곡차곡 쌓는 형태.

집적회로 부품의 역할 :

- 트랜지스터는 전원을 켜고 끄는 스위치 역할

- 캐패시터는 전하를 충전해 보관하는 창고 역할

- 저항은 전류의 흐름을 조절

- 다이오드는 신호를 고르게 전하는 역할

BJT, 양방향 접합형 트랜지스터의 한계와 해결책

- 제조가 까다롭고 전력 소모가 컸던 양방향 접합형 트랜지스터 (Bipolar Junction Transistor)의 문제점

- 1960년 벨 연구소 강대원 박사와 마틴 아탈라가 ‘금속 산화막 반도체 전계효과 트랜지스터(MOS-FET, Metal Oxide Semiconductor Field Effect Transistor)’를 개발

[반도체 8대 공정] 3탄, 전자산업의 혁명! 집적회로

@삼성반도체이야기

https://bit.ly/3voZ7DM

2. 제조 공정

시장조사 -> 설계 -> 제조

반도체 제조사의 시장조사 :

- 고객사의 수요를 파악.

(적정 메모리 용량, 감내 가능 전력 소비량, CPU 전력 및 발열 한도, CPU 성능 등)

칩 설계 :

- 시장 요구사항을 반영한 디자인. 트랜지스터 및 소형 부품의 연결관계 및 위치 조정.

* 메모리(D램)의 구성 : 데이터 저장이 목적.

[ 명령 및 주소 수신 부품 / 주소 해독 부품 / 데이터 저장소 / 래치(데이터 임시 저장소) ]

- 명령 종류(Read, Write), 주소, 데이터를 받아 명령을 수행. 간단한 구성으로 설계 난이도 낮음.

- 데이터 저장소 면적 감소를 통한 크기 싸움이 관건. 신형 노광기 도입 등으로 경쟁.

* CPU의 구성 : 연산이 목적. 수많은 부품의 복잡한 연결형태로 구성.

[ 다층 캐시 메모리, 디코더, ROB, 대기소, 연산포트, ALU 등 ]

- 각기 다른 구조의 명령어 조합으로 구성되어 트랜지스터 밀도 높음.

- 설계 난이도 높음.

- 명령어가 다양해 신호 처리 복잡도가 높으므로, 지속적으로 신규 기능을 칩 내부에 추가

- 설계 보조 프로그램 EDA, PDK 등을 활용

제조

- 팹(반도체 공장)에서 반도체 제조.

- 판 위에서 구조물을 층층이 만들어내는 방식

- 아래의 과정을 600스텝 이상 반복. 물질 및 포토레지스트 도포 과정 중 베이킹도 진행.

1. 웨이퍼(판) 준비

2. 웨이퍼 위에 물질 도포

3. 물질 위에 포토레지스트 도포

4. 고성능 광원 차단 마스크를 준비

5. 마스크를 위치시킨 뒤 강력한 광원으로 포토레지스트 태우기 - 마스크 아래 포토레지스트만 보존

6. 식각 (가스로 물질 깎아내기) - 마스크 아래 포토레지스트가 남은 부분은 식각되지 않음

7. 세척해 식각되지 않은 잔여 포토레지스트 제거

** 포토레지스트 : 광원에 대한 반응성인 높아 잘 타지만, 깍는 식각 과정에는 저항성이 높음.

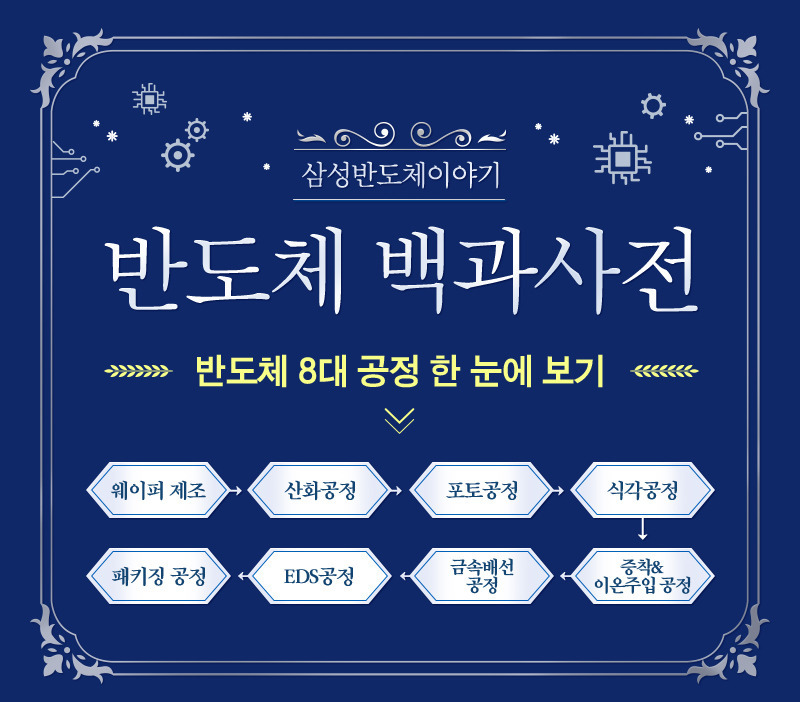

[반도체 백과사전] 반도체 8대 공정 한 눈에 보기 [요약본]

1. 웨이퍼 제조 (실리콘 잉곳 생성 및 절단, 연마)

2. 산화 공정 (절연막 역할의 산화막 생성)

3. 포토 공정 (감광액 도포, 노광, 현상을 통한 회로 그리기)

4. 식각 공정 (플라즈마 식각 등으로 불필요 막질 제거)

5. 증착 및 이온주입 공정 (박막 입혀 구분/보호 + 불순물 주입으로 전도성 부여)

6. 금속 배선 공정 (회로 패턴 따라 배리어 메탈 및 금속 배선(전기선) 증착)

7. EDS 공정 (프로브카드 기반 품질 테스트, 불량 판정 및 수선)

8. 패키징 공정 (골격 내 조립, 기판과의 연결, 밀봉 및 성형 등)

https://www.samsungsemiconstory.com/kr/%EB%B0%98%EB%8F%84%EC%B2%B4-%EB%B0%B1%EA%B3%BC%EC%82%AC%EC%A0%84-%EB%B0%98%EB%8F%84%EC%B2%B4-8%EB%8C%80-%EA%B3%B5%EC%A0%95-%ED%95%9C-%EB%88%88%EC%97%90-%EB%B3%B4%EA%B8%B0/

1. 웨이퍼 제조 : 반도체 집적회로 주재료인 웨이퍼 제조

반도체 집적회로란, 다양한 기능을 처리하고 저장하기 위해 많은 소자를 하나의 칩 안에 집적한 전자부품을 말합니다. 웨이퍼라는 얇은 기판 위에 다수의 동일 회로를 만들어 반도체 집적회로가 탄생되는 만큼, 웨이퍼는 반도체의 기반인 셈이죠. 웨이퍼는 실리콘(Si), 갈륨 아세나이드(GaAs) 등을 성장시켜 만든 단결정 기둥을 적당한 두께로 얇게 썬 원판을 의미하는데요. 대부분의 웨이퍼는 모래에서 추출한 규소, 즉 실리콘으로 만듭니다.

1-1. 잉곳 생성 :

실리콘 원료 정제를 위해 융해 후 고순도 용액을 결정 성장 시켜 굳힌 실리콘 기둥, 잉곳을 생산.

1-2. 잉곳 절단 :

팽이 모양 잉곳을 원판형 웨이퍼로 만들기 위한 균일 두께의 얇은 원판으로의 절단.

얇을수록 제조 원가 절감. 지름이 클수록 개당 반도체 칩 수 증가.

1-3. 웨이퍼 표면 연마 (IC 칩 생산) :

연마액 및 연마 장비로 가공 전 웨이퍼(베어 웨이퍼)를 가공해 표면에 IC를 형성

[반도체 8대 공정] 1탄, ‘웨이퍼’란 무엇일까요? @삼성반도체이야기

https://bit.ly/3gl7njV

2. 산화 공정 : 웨이퍼 표면 내 실리콘 산화막 형성

웨이퍼는 전기가 통하지 않는 부도체 상태입니다. 그래서 도체와 부도체의 성격을 모두 가진 ‘반도체’의 성질을 가질 수 있도록 만드는 작업이 필요한데요. 이를 위해 웨이퍼 위에 여러 가지 물질을 형성시킨 후 설계된 회로 모양대로 깎고, 다시 물질을 입혀 깎아내는 일이 반복되죠. (...) 산화공정을 거치는 이유는 웨이퍼에 절연막 역할을 하는 산화막(SiO₂)을 형성해 회로와 회로사이에 누설전류가 흐르는 것을 차단하기 위해서 입니다. 산화막은 또한 이온주입공정에서 확산 방지막 역할을 하고, 식각공정에서는 필요한 부분이 잘못 식각되는 것을 막는 식각 방지막 역할도 합니다.

웨이퍼에 막을 입히는 산화공정의 방법에는 열을 통한 열산화(Thermal Oxidation), 플라즈마 보강 화학적 기상 증착(PECVD), 전기 화학적 양극 처리 등 여러 종류가 있습니다. 그 중 가장 보편적인 방법은 800~1,200℃의 고온에서 얇고 균일한 실리콘 산화막을 형성시키는 열산화 방법입니다. 열산화 방법은 산화반응에 사용되는 기체에 따라 건식산화(Dry Oxidation)와 습식산화(Wet Oxidation)로 나뉘는데요.

열산화 방법은 산화반응에 사용되는 기체에 따라 건식산화(Dry Oxidation)와 습식산화(Wet Oxidation)로 나뉘는데요. 건식산화는 순수한 산소(O₂)만을 이용하기 때문에 산화막 성장속도가 느려 주로 얇은 막을 형성할 때 쓰이며, 전기적 특성이 좋은 산화물을 만들 수 있습니다. 습식 산화는 산소(O₂)와 함께 용해도가 큰 수증기(H₂O)를 함께 사용하기 때문에 산화막 성장속도가 빠르고 보다 두꺼운 막을 형성할 수 있지만, 건식 산화에 비해 산화층의 밀도가 낮습니다. 보통 동일한 온도와 시간에서 습식산화를 통해 얻어진 산화막은 건식산화를 사용한 것보다 약 5~10배 정도 더 두껍습니다.

[반도체 8대 공정] 2탄, 웨이퍼 표면을 보호하는 산화공정 @삼성반도체이야기

https://bit.ly/2TvBzQj

3. 포토 공정 : 웨이퍼 위 반도체 회로 그려넣기

포토 리소그래피(Photo Lithography)를 줄여서 포토공정(Photo)이라고 하는데요. 이 공정은 웨이퍼 위에 회로 패턴이 담긴 마스크 상을 빛을 이용해 비춰 회로를 그리기 때문에 붙여진 이름입니다.

3-1. 준비 단계

- 컴퓨터 시스템(CAD, computer-aided design)을 이용해 웨이퍼에 그려 넣을 회로를 설계

- 전자회로 패턴(Pattern)으로 설계되는 도면에 엔지니어들이 설계한 정밀회로를 담음

- 그 정밀도가 반도체의 집적도를 결정

3-2. 포토마스크 만들기

- 순도가 높은 석영(Quartz)을 가공해 기판을 제작

- 설계된 회로 패턴(Pattern)은 기판 위에 크롬(Cr)으로 미세 회로를 형상화

3-3. 감광액 도포

- 웨이퍼 표면에 빛에 민감한 물질인 감광액(PR, Photo Resist)을 골고루 바르는 작업

3-4. 노광

- 노광장비(Stepper)를 사용해 회로 패턴이 담긴 마스크에 빛을 통과시켜 웨이퍼에 회로를 그려 넣음

- 반도체 공정에서의 노광은 빛을 선택적으로 조사하는 과정

3-5. 현상

- 웨이퍼에 현상액을 뿌려 가며 노광된 영역과 노광 되지 않은 영역을 선택적으로 제거해 회로 패턴을 형성

- 웨이퍼 위에 균일하게 입혀진 감광액(PR)은 빛에 어떻게 반응하는가에 따라 양성 혹은 음성으로 분류

- 양성 감광액의 경우 노광 되지 않은 영역을 남김

- 음성 감광액의 경우 노광된 영역만 남겨 사용

[반도체 8대 공정] 4탄, 웨이퍼에 회로를 그려 넣는 포토공정 @삼성반도체이야기

https://bit.ly/3cGxWOh

4. 식각 공정 : 반도체 구조 형성 패턴 제조 과정 (필요 회로 패턴 외 제거)

- 식각 공정에서 감광액이 없는 산화막 부분을 제거

- 영문명 = Etching

- 웨이퍼에 액체 또는 기체의 부식액(etchant)을 이용해 불필요한 부분을 선택적으로 제거

- 식각이 끝나면 감광액도 제거

- 반도체를 구성하는 여러 층의 얇은 막에 원하는 회로 패턴을 형성하는 과정을 반복

- 식각 반응을 일으키는 물질의 상태에 따라 습식, 건식으로 분류

- 건식 식각(Dry Etching)은 반응성 기체, 이온 등을 이용해 특정 부위를 제거

- 습식 식각(Wet Etching)은 용액을 이용 화학적인 반응을 통해 식각

- 건식은 습식에 비해 비용이 비싸고 방법이 까다로운 단점이 있음

- 최근에는 나노 단위로 고집적화되는 반도체 기술 변화에 따라 회로선폭 역시 세밀화

- 최근 수율을 높이기 위한 방법으로 습식(Wet)보다는 건식(Dry) 식각이 확대

- 건식 식각은 플라즈마(Plasma) 식각

건식식각 (1) 일반 대기압보다 낮은 압력인 진공 챔버(Chamber)에 가스를 주입

건식식각 (2) 전기 에너지를 공급하여 플라즈마를 발생

건식식각 (3) 플라즈마로 발생한 반응성 원자의 막질 제거

** 플라즈마는 이온화된 기체.

** 이온화는 전기적으로 중성인 원자 또는 분자가 전자를 떼어 내거나 추가 확보함으로써, 양전하 또는 음전하 상태로 바뀌는 현상.

** 플라즈마는 전기에너지에 의해 형성된 충분한 크기의 자기장이 기체에 가해질 때, 기체가 충돌하고 이온화됨으로써 발생. 자기장이 자유전자를 가속화시켜 높은 에너지를 가진 자유전자가 중성의 원자나 분자와 충돌하여 이온화.

** 이온화에 의해 생성된 추가 전자도 연쇄 반응(Avalanche)에 의해 또 다른 이온화를 일으키면서 이온의 수가 기하급수적으로 증가.

** 플라즈마 상태에서 해리된 반응성 원자(Radical Atom)가 웨이퍼 위를 덮고 있는 막질 원자와 만나 강한 휘발성을 띠면서 표면에서 떨어져 나감. 감광액(PR, Photo Resist) 보호막으로 가려져 있지 않은 막질을 제거.

건식식각 유의점 = 균일도, 속도, 선택비, 형상 등

건식식각 유의점 (1) 균일도(Uniformity)를 유지 : 웨이퍼의 부위에 따라 식각 속도가 다를 경우, 형성된 모양이 부위별로 다르게 되어 특정 부위에 위치한 칩에 불량이 발생하거나 특성이 달라지는 문제

건식식각 유의점 (2) 식각 속도(Etch Rate) : 속도 영향 요인의 조절 능력을 높여 전체적인 수율을 향상

[반도체 8대 공정] 5탄, 반도체 회로패턴의 완성 ‘식각 공정’ @삼성반도체이야기

https://bit.ly/3zcUIHq

5. 증착 및 이온주입 공정

- 증착 공정 : 회로 간 구분, 연결, 보호 역할의 박막을 제조

- 이온 주입 : 반도체가 전기적 특성을 갖도록 만듦

- 반도체의 원재료가 되는 단결정 실리콘(Si) 웨이퍼 위에 단계적으로 박막을 입히고 회로를 그려 넣는 포토공정을 거쳐 불필요한 부분을 선택적으로 제거하는 식각공정과 세정하는 과정을 여러 번 반복

- 박막(Thin film) = 회로 간의 구분과 연결, 보호 역할을 하는 얇은 막

- 단순한 기계 가공으로는 실현 불가능한 1마이크로미터(μm, 100만 분의 1미터) 이하의 얇은 막

- 박막 구성 (1) 금속막(전도)층 = 크게 회로들 간 전기적인 신호를 연결

- 박막 구성 (2) 절연막층 = 내부 연결층을 전기적으로 분리하거나 오염원으로부터 차단

- 증착(Deposition) = 웨이퍼 위에 원하는 분자 또는 원자 단위의 박막을 입히는 일련의 과정

증착 방법 (1) 물리적 기상증착방법(PVD, Physical Vapor Deposition)

- 금속 박막의 증착에 주로 사용되며 화학반응이 수반되지 않음

증착 방법 (2) 화학적 기상증착방법(CVD, Chemical Vapor Deposition)

- 가스의 화학 반응으로 형성된 입자들을 외부 에너지가 부여된 수증기 형태로 쏘아 증착

- 도체, 부도체, 반도체의 박막증착에 모두 사용될 수 있는 기술

- 현재 반도체 공정에서 주로 사용

- 사용하는 외부 에너지에 따라 열 CVD, 플라즈마 CVD, 광 CVD로 세분화

- 플라즈마 CVD는 저온에서 형성이 가능하고 두께 균일도를 조절할 수 있으며 대량 처리가 가능하다는 장점 때문에 가장 많이 이용

- 이온주입공정 = 불순물을 넣어줘 반도체가 전기적인 성질, 전류를 흐르게 하는 전도성을 가지게 하는 공정

- 이온(불순물)을 미세한 가스입자로 만들어 원하는 깊이만큼 웨이퍼 전면에 균일하게 주입

- 불순물로는 15족 원소 인(P), 비소(As), 13족 원소 붕소(B) 등을 사용

- 15족 원소를 주입하면 n형 반도체

- 13족 원소를 주입하면 p형 반도체

[반도체 8대 공정] 6탄, 반도체에 전기적 특성을 입히다! 증착&이온주입 공정 @삼성반도체이야기

https://bit.ly/352QXWY

6. 금속 배선 공정

- 신호가 잘 전달되도록 반도체 회로 패턴에 따라 전기길(금속선)을 연결하는 작업

- 반도체의 회로 패턴을 따라 금속선(Metal Line)을 이어주는 과정

- 금속선 재료 필요 조건 : 웨이퍼와의 부착성, 낮은 전기저항, 열적/화학적 안정성, 패턴형성 용이성, 작아도 끊김 없는 신뢰성, 낮은 제조가격

- 조건 충족 재료 = 알루미늄(Al), 티타늄(Ti), 텅스텐(W) 등

- 배리어 메탈 증착의 필요성

* 알루미늄(Al)은 실리콘(Si)과 만나면 서로 섞이려는 성질

* 실리콘 웨이퍼의 경우 알루미늄 배선 과정에서 접합면이 파괴되는 현상 발생

* 접합면 파괴 방지 위해 알루미늄과 웨이퍼 접합면 사이 장벽 역할 금속, 베리어 메탈 증착

- 금속 배선 역시 증착을 통해 진행

* 금속을 진공 챔버에 넣고 낮은 압력에서 끓이거나 전기적 충격을 주어 금속을 증기 상태로 변화

* 웨이퍼를 진공 챔버에 넣으면 얇은 금속막이 형성

* 금속 배선 공정에서도 좁은 영역에 균일한 박막을 형성시키기 위해 화학적 기상증착(CVD)으로의 전환 중

[반도체 8대 공정] 7탄, 전기가 통하는 길을 만드는 ‘금속 배선 공정’ @삼성반도체이야기

https://bit.ly/3pywWAY

7. EDS 공정(Electrical Die Sorting)

- 전기적 특성검사를 통해 개별 칩들이 원하는 품질 수준에 도달했는지를 확인하는 공정

* 목적 1) 웨이퍼 상태 반도체 칩의 양품/불량품 선별

* 목적 2) 불량 칩 중 수선 가능한 칩의 양품화

* 목적 3) FAB 공정 또는 설계에서 발견된 문제점의 수정

* 목적 4) 불량 칩을 미리 선별해 이후 진행되는 패키징공정 및 테스트 작업의 효율 향상

- 과정 1) 전기적 특성검사를 통해 각각의 칩들이 원하는 품질 수준에 도달하는지 체크

- 과정 2) 양품 가능 여부를 판단

- 과정 2-1) 수선(Repair) 가능한 칩은 다시 양품으로 만들기

- 과정 2-2) 불가능한 칩은 특정 표시(Inking)를 통해 불량으로 판정

- 기술

* 프로브 카드(Probe Card)에 웨이퍼를 접촉시켜 진행

* 프로브 카드에 있는 수많은 미세한 핀(Pin)이 웨이퍼와 접촉해 전기를 보내고 그 신호를 통해 불량 칩을 선별

- 공정 단계

공정 (1) ET Test & WBI(Electrical Test & Wafer Burn In)

* ET Test(Electrical Test) = 반도체 집적회로(IC) 동작에 필요한 개별소자들(트랜지스터, 저항, 캐패시터, 다이오드)에 대해 전기적 직류전압, 전류특성의 파라미터를 테스트하여 동작 여부를 판별

* WBI공정(Wafer Burn In) = 웨이퍼에 일정 온도의 열을 가한 다음 AC(교류)/DC(직류) 전압을 가해 제품의 결합, 약한 부분 등 잠재적인 불량 요인을 파악

공정 (2) Hot/Cold Test

* 전기적 신호를 통해 웨이퍼 상의 각각의 칩 중 불량품이 있는지 판정

* 수선 가능한 칩은 수선 공정에서 처리하도록 정보를 저장

* 특정 온도에서 정상적으로 동작하는지 판별하기 위해 상온보다 높고 낮은 온도의 테스트

공정 (3) Repair / Final Test (양/불량을 최종 판단)

* Hot/Cold 공정에서 수선 가능으로 판정된 칩들을 수선

* 수선이 끝나면 Final Test 공정을 통해 수선이 제대로 이루어졌는지 재차 검증

공정 (4) Inking

* 불량 칩에 특수 잉크를 찍어 육안으로도 불량을 식별할 수 있도록 만드는 공정

* 과거의 Inking 공정은 불량 칩에 직접 잉크를 찍었으나 현재는 Data만으로 양/불량을 판별할 수 있도록 처리

* 조립 및 검사 공정에서 사용되는 원부자재, 설비, 시간, 인원 등의 손실 절감 효과

7.5 건조(Bake)된 후, QC(Quality Control) 검사를 거쳐 조립공정으로

[반도체 8대 공정] 8탄, 완벽한 반도체로 태어나기 위한 첫 번째 테스트 ‘EDS공정’ @삼성반도체이야기

https://bit.ly/3glnEoZ

8. 패키징 공정

- 반도체를 외부환경으로부터 보호하고, 전기적으로 연결

- 완성된 웨이퍼의 반도체 칩을 하나하나 잘라내 베어칩(bare chip) =다이(die)를 제조

- 이 상태의 칩은 외부와 전기신호를 주고받을 수 없으며, 외부 충격에 의해 손상되기 쉬움

- 패키징(Packaging) = 반도체 칩이 외부와 신호를 주고 받을 수 있도록 길을 만들어주고 다양한 외부환경으로부터 안전하게 보호받는 형태로 만드는 과정

- 패키징 (1) 웨이퍼 절단 : 웨이퍼를 낱개의 칩으로 분리

* 스크라이브 라인을 따라 웨이퍼를 다이아몬드 톱이나 레이저 광선을 이용해 절단

* ‘웨이퍼 소잉(Wafer Sawing)’ = ‘다이싱(Dicing)’

- 패키징 (2) 칩 접착(Die attach) : 리드프레임(골격)에 접착

* 절단된 칩들은 리드프레임(Lead Frame) 또는 PCB(Printed Circuit Board) 위로 이동

* 리드프레임은 반도체 칩과 외부 회로 간 전기신호를 전달하고, 외부 환경으로부터 칩을 보호, 지지해주는 골격 역할

- 패키징 (3) 금선 연결 : 칩과 기판을 연결

* 반도체의 전기적 특성을 위해 기판 위에 올려진 반도체 칩의 접점과 기판의 접점을 가는 금선을 사용하여 연결하는 공정

** 금선 연결 방식 (1) 와이어 본딩 ) 기판과 칩을 전선으로 직접 연결

** 금선 연결 방식 (2) 플립칩 패키지 기술 ) 반도체의 속도를 향상시키기 위해 칩의 회로와 기판을 직접 볼 형태의 범프(Bump, 돌기)로 연결. 와이어본딩보다 전기 저항이 작고 속도가 빠르며, 작은 폼팩터(Form Factor) 구현이 가능. 범프의 소재로는 주로 금(Au) 또는 솔더(Solder, 주석/납/은 화합물) 사용.

- 패키징 (4) 성형(Molding) 공정 : 보호 + 형태 조정을 위한 밀봉

* 열, 습기 등의 물리적인 환경으로부터 반도체 집적회로를 보호하고, 원하는 형태의 패키지로 만듦

* 금선 연결까지 끝난 반도체 칩을 화학 수지로 밀봉하는 공정

8.5 패키지 테스트(Package Test)

- 패키징 공정이 완료되면 반도체 제품의 최종 불량유무를 선별

- 완제품 형태를 갖춘 후에 검사를 진행하기 때문에 ‘파이널 테스트(Final Test)’라고도 부름

- 반도체를 검사장비(Tester)에 넣고 다양한 조건의 전압이나 전기신호, 온도, 습도 등을 가해 제품의 전기적 특성, 기능적 특성, 동작 속도 등을 측정

- 테스트 데이터를 분석해 제조공정이나 조립공정에 피드백함으로써 제품의 질을 개선

[반도체 8대 공정] 9탄, 외부환경으로부터 반도체를 보호하는 패키징 (Packaging) 공정 @삼성반도체이야기

https://bit.ly/3cED9q5

[출처: 삼성반도체이야기]

https://www.samsungsemiconstory.com/kr/